本文介紹的解決方案採用數位零電壓切換(ZVS)控制器-XDPS21081平台,可達到21W/in3功率密度(不含外殼)。本65W參考設計採用通用AC輸入,並將其轉換為USB-PD 3.0通訊協定所支援的一般5至20V DC輸出,此通訊協定已廣泛用於現代大多數的筆記型電腦和智慧型手機中。使用諧振切換轉移幾乎可消除所需頻段中的主MOSFET切換損耗。

這種方法可達到所需的高切換頻率,以允許使用更小型的元件(即變壓器),同時仍可維持(甚至提高)在較小型尺寸中管理散熱所需的效率。簡而言之,在所有負載與線路範圍內,總體效率可提高至90%以上,且峰值效率可達到93%以上。

USB-PD應用的65W充電器參考設計

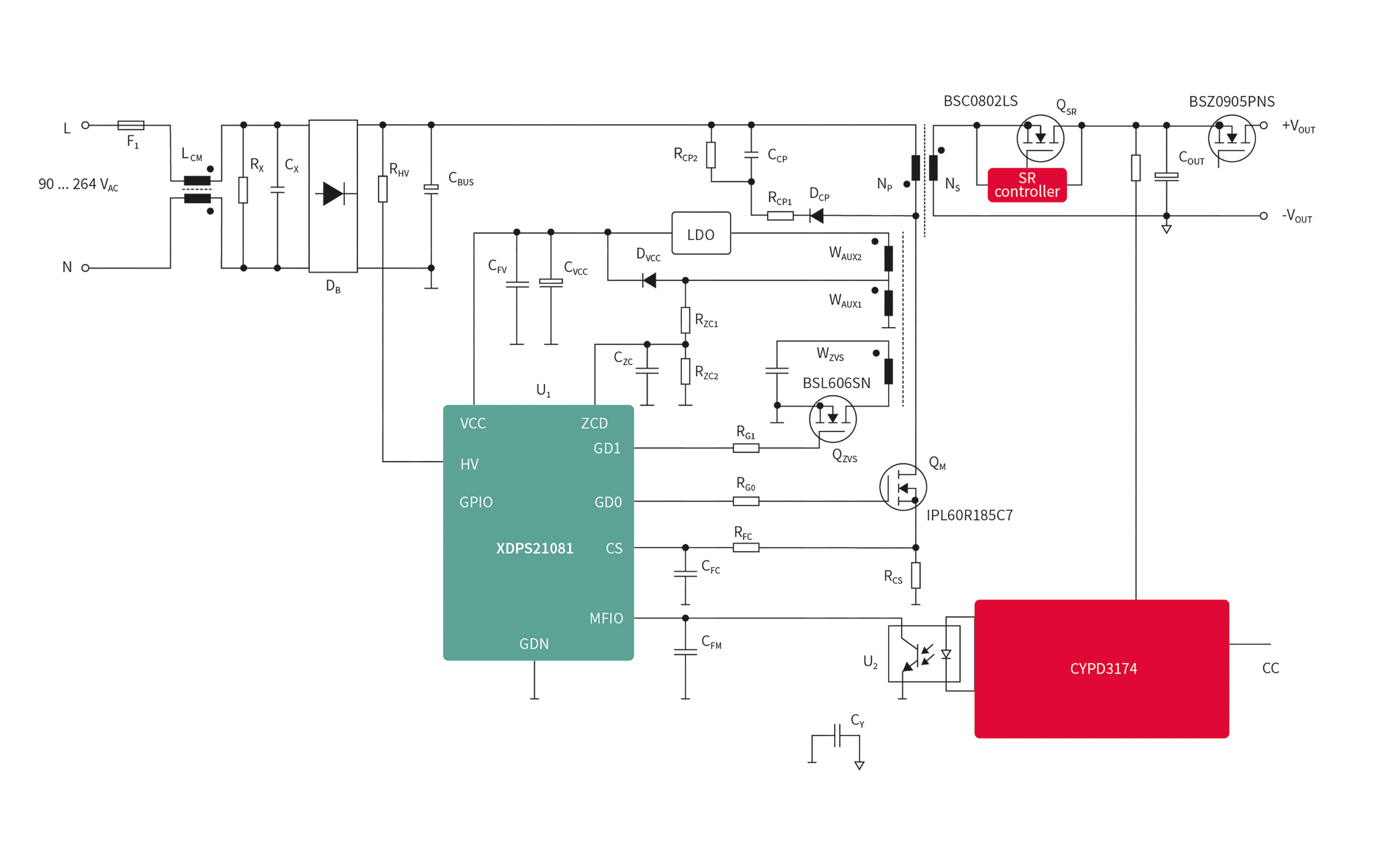

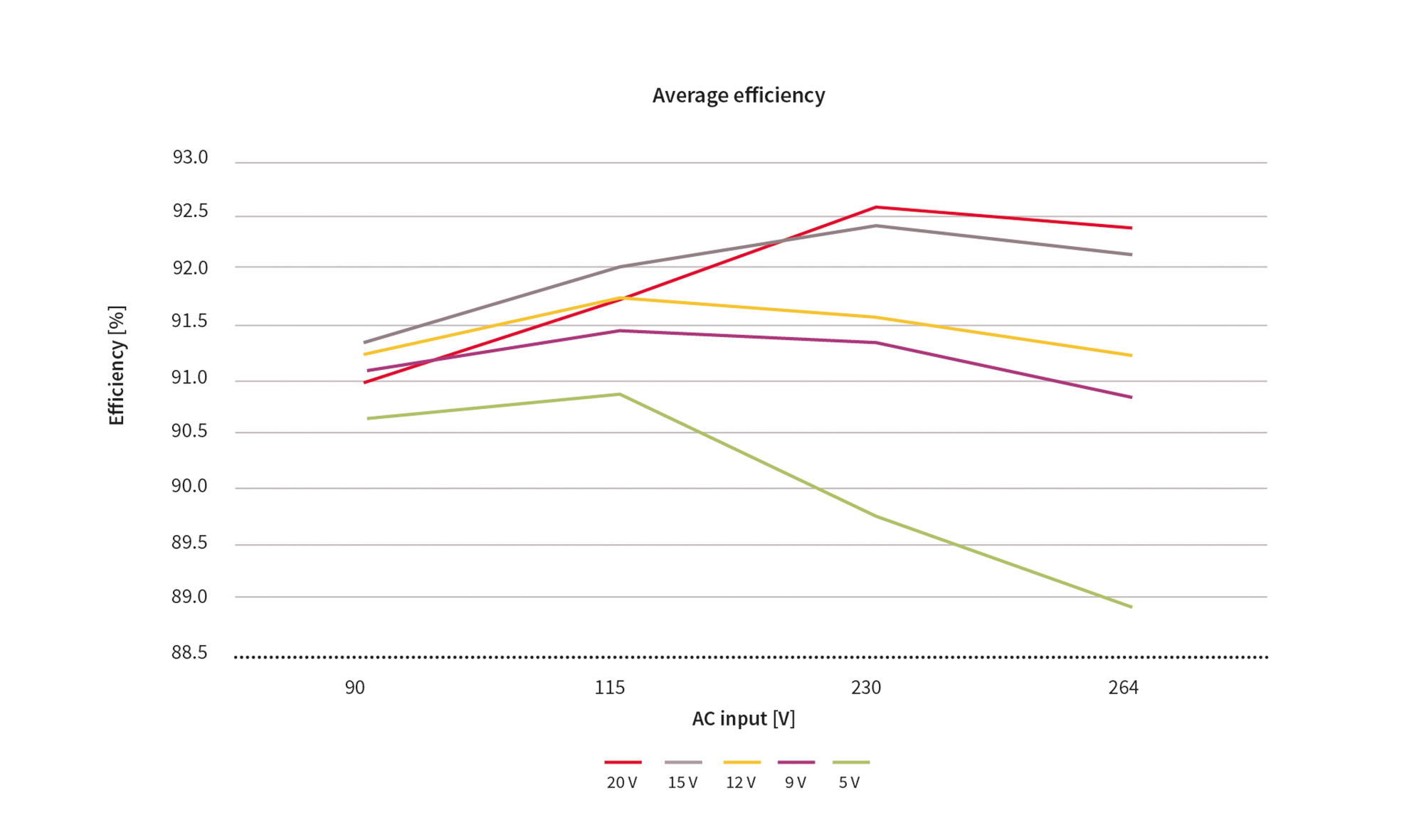

此解決方案接受從90V AC至265V AC的寬輸入範圍,而輸出可為5V至20V,而最大輸出功率為65W(圖1)。選擇返馳式拓撲和商品元件是為了平衡成本、效能或製造等因素。ZVS是由PWM控制器XDPS21081 GD1針腳驅動的額外ZVS繞組及ZVS電路啟動。 藉由ZVS功能的協助,高壓線路的切換損耗會大幅降低,因此可將切換頻率設定在約140kHz。若為低壓線路,此系統能在重負載下以準諧振(QR)模式運作,因此可產生自然的ZVS效應以減少功率耗損。降頻模式(FRM)與主動式爆發模式(ABM)執行後,可在中負荷與輕負荷下維持高效率。圖2說明在不同狀況下的效率。

圖1 65W USB-PD充電器方塊圖

圖1 65W USB-PD充電器方塊圖

圖2 四點效率,超越調節要求。

圖2 四點效率,超越調節要求。

在XDPS21081 HV針腳和大電容器之間連接電阻器,即可啟動關斷功能。此外,本設計具備各種保護功能,例如OCP、Vout OVP、VCC OVP、OLP、OTP、閂鎖啟用及電源開啟前的CS針腳短路保護。

快速充電器設計拓撲選擇

由於準諧振返馳式拓撲具備高成本效益比,目前已廣泛應用於充電器市場中。採用此拓撲後,波谷切換可減少切換損耗,且這種單磁元件拓撲也可帶來成本優勢。儘管QR需隨著充電器功率增加而提高,但無法保證在完整電壓輸入範圍內能執行零電壓導通。特別是在高電壓輸入期間,MOSFET的高VDS會造成明顯的切換功率損耗,因此無法支援高頻率運作。由於高電壓輸入與低電壓輸入之間的運作頻率差異極大,因此難以將變壓器設計最佳化。

近年採用主動式箝制返馳式(ACF)拓撲,藉以改善充電器內的功率密度。ACF可利用變壓器漏感能量來提高效率,亦即將此漏感能量儲存在電容器箝制中,然後在後續的切換循環中將其傳送至輸出端。控制箝制後,即可在FET上達到零電壓切換,並藉由消除另一個主要損耗來源,以便進一步提高效率。這可提供更高的切換頻率及縮減電源供應器的尺寸。為了確保零電壓導通,即使在輕負載狀態下,仍需要諧振循環電流。但是,這種諧振循環電流將會造成額外損耗,因此會降低平均效率。與QR返馳式的情況相似,頻率在高壓線路和低壓線路輸入期間的差異極大,將會使變壓器設計成為一大挑戰。

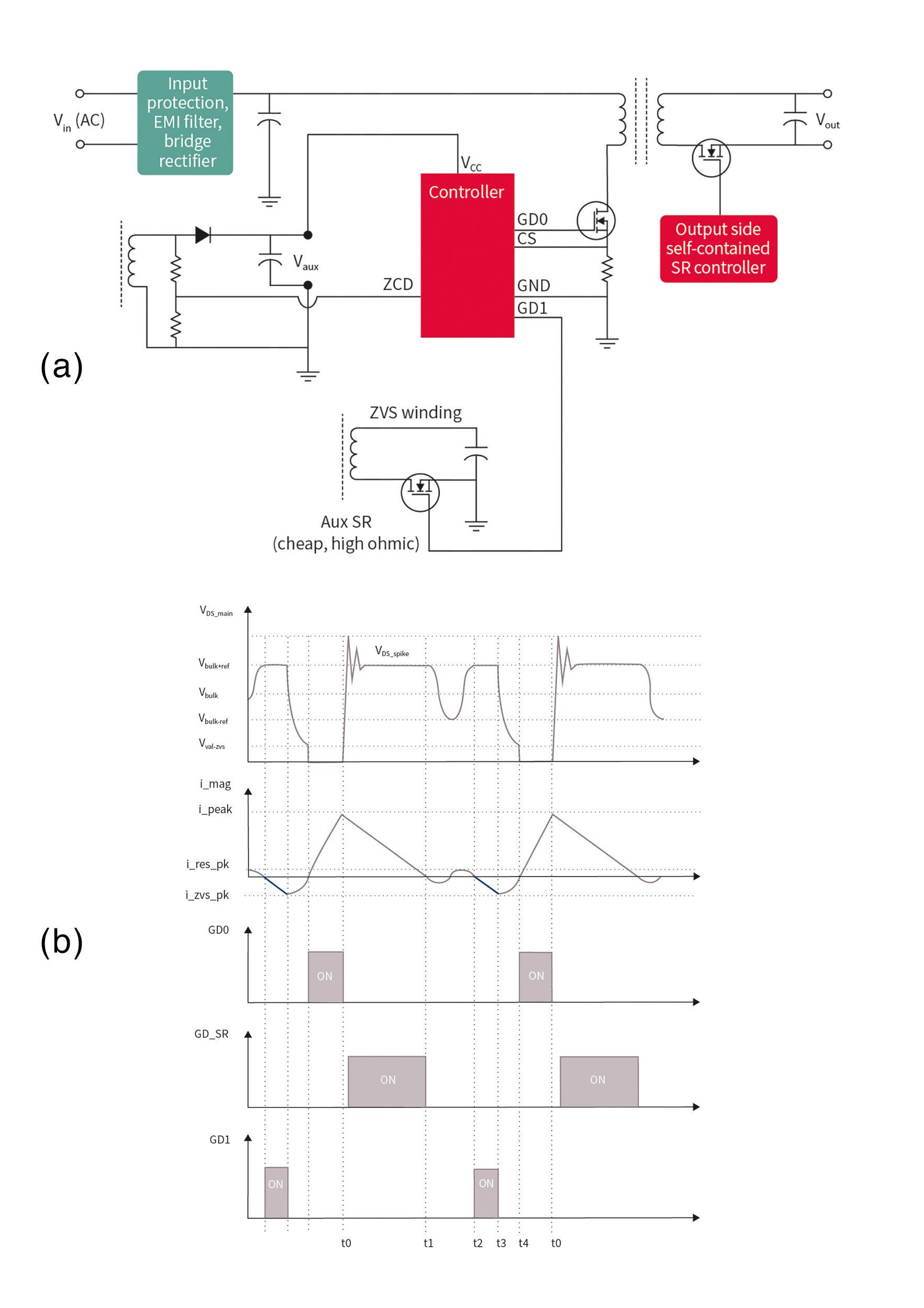

為了將返馳式效能最佳化,有業者如英飛凌(Infineon)推出了強制頻率諧振(FFR)返馳式。這種拓撲擁有數個出色的效能特色,包括但不限於零電壓導通、外部元件數量減少,以及在高壓線路與低壓線路輸入運作期間的頻率差異較小。圖3說明了此拓撲與ZVS的運作原理。

圖3 建議採用的FFR ZVS拓撲(a)與ZVS運作原理(b)

圖3 建議採用的FFR ZVS拓撲(a)與ZVS運作原理(b)

將主MOSFET在t0關閉後,同步整流(SR)MOSFET將會因短暫的遮沒時間而稍微延遲啟動。至於t1,當消磁電流依照理想歸零時,SR MOSFET會隨即關閉,然後將電感Lp與Ceqv振盪磁化。主MOSFET的電壓將會從Vbulk+Vref振盪至Vbulk-Vref。若輔助MOSFET在t2啟動,則主MOSFET的諧振峰值代表磁化電流為零,因此i_mag值將累積為負值。在此受控的ZVS接通時間期間,主MOSFET的VDS會箝制於Vbulk+Vref。一旦峰值電流達到i_zvs_pk後,輔助MOSFET隨即關閉,且由於此電流儲存於磁化電感中且為反方向,因此其將繼續朝該方向流動,並釋放儲存在Ceqv中的能量。IC中的這段期間是由可設定的tZVSdead參數所控制。因此,在t4時,主MOSFET的洩流電壓將會達到最小值,並開啟主MOSFET,可大幅減少導通損耗,幾乎等同於ZVS。如圖3所示,能量會與Vbulk成正比,ZVS接通時間亦是如此。

ZVS脈衝插入是以Nano-DSP核心與記憶資訊為基礎。IC可辨識下一個切換循環的週期、ZVS停滯時間與ZVS脈衝接通時間。因此,假設IC主閘極導通時間也是固定時間,從切換週期將這兩個部分(ZVS停滯時間與ZVS脈衝接通時間)減去後,就能判定ZVS脈衝的起點。當CS訊號達到目前命令時,也可判定主閘極停止點。

進行密度設計時的MOSFET封裝考量

除了選擇合適的拓撲外,選擇正確的高電壓MOSFET也是呈現高效率設計的關鍵。如英飛凌的CoolMOS系列具備持續提高的效能,有助於減少切換損耗。由於減少了MOSFET的總閘極電荷(Qg)及輸出電容所儲存的能量(這些能量(Eoss)必須在硬切換期間的每個循環中釋放),因此得以改善MOSFET的切換損耗。透過減少每個切換循環中耗散的總電荷,即可提高此系統在輕負載時的效率。由於CoolMOS技術持續改進,使MOSFET的傳導損耗得以降低,並使裝置的溫度係數也不斷提高。隨著傳導損耗與切換損耗有所改善,新技術為轉變至更高RDS(on)的MOSFET帶來可能,進而降低整體系統成本或提高整體系統切換頻率,這可減少外形尺寸與數量,因此也降低了被動元件的成本。

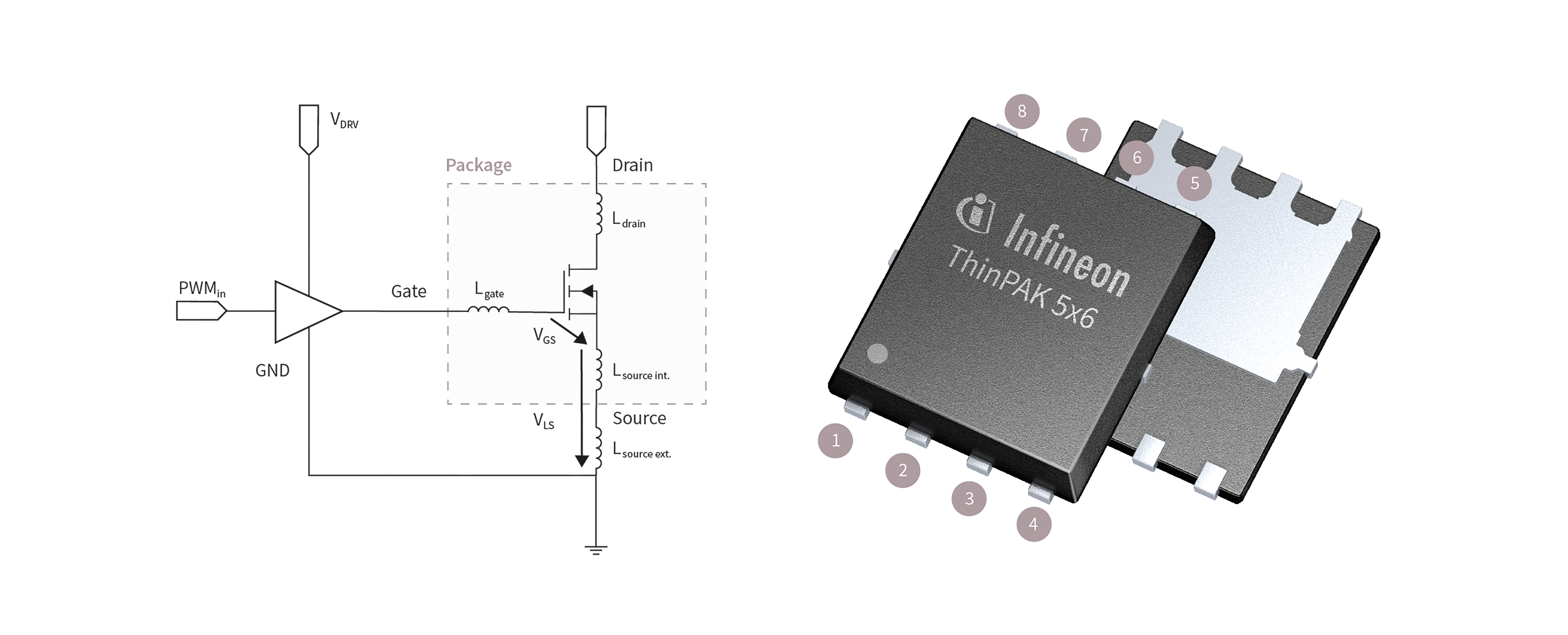

在充電器設計中,MOSFET的總迴路電感(由閘極-源極與汲極-源極電感所組成)對於避免MOSFET再次導通與減少EMI至關重要。與DPAK或FullPAK THD封裝相比,ThinPAK的閘極、汲極與源極電感皆有所減少(如圖4所示)。與DPAK封裝相比,ThinPAK的內部源極電感也減少了63%。

圖4 ThinPAK封裝可減少閘極驅動迴路中的寄生電感

圖4 ThinPAK封裝可減少閘極驅動迴路中的寄生電感

為減少MOSFET閘極上的鈴振,總閘極源極電感(Lgate_loop=Lsource+Lgate)相當重要。當由閘極電容(Ciss)和總閘極迴路電感(Lsource ext.+Lgate_loop)所形成的LC諧振槽受到方波驅動波形的激發時,可能會造成MOSFET閘極上的鈴振。減少總Lgate_loop即可減少MOSFET閘極上的鈴振。

藉由數位ZVS控制器如XDPS21081,在低壓線路電壓輸入期間執行QR,並在高壓線路電壓輸入期間執行FFR,使得此65W參考設計可呈現高達93%的效率。將此控制器搭配ThinPAK內的CoolMOS超接面MOSFET來使用,即可將充電器置入小型外殼內。此外,簡化的EMI濾波器設計與低BOM成本有助於設計工程師提高充電器設計能力。

(本文作者為英飛凌科技全球低功率SMPS應用部門協理)