處理雜訊和電磁干擾,是任何高速數位設計都無法迴避的問題,尤其以數位訊號處理器(DSP)為基礎的影音和通訊訊號處理系統,特別容易受到影響。且受到雜訊及電磁干擾,更可能影響DSP系統操作或造成設計無法通過美國聯邦通訊委員會(FCC)認證。因此設計人員應先了解潛在的雜訊和電磁輻射來源,並在設計初期就將干擾降到最低。若能進行聰明的事前規畫,將能省下大量的除錯及修改時間,進而節省整體的時間與成本。

目前最快速DSP的內部時脈頻率已超過1GHz,並能以數百MHz的速率傳送和接收訊號。這些快速切換的訊號會產生龐大的雜訊及電磁輻射,進而降低系統效能和造成嚴重的電磁干擾。除此之外,DSP系統也變得更為複雜,大多內含音訊和視訊介面、液晶顯示器(LCD)、無線通訊、乙太網路和USB控制器、電源供應、振盪器、驅動控制和其他電路等,而這些都可能產生雜訊或受鄰近元件干擾。尤其以影音系統特別容易受到這些問題的影響而造成效能下降。

從設計源頭解決雜訊問題

要避免這些困擾,最好是在設計之初就著手解決雜訊和電磁輻射問題。許多新設計第一次都無法通過FCC的電磁相容性認證測試,其實只要在開始設計時多花一點時間在低雜訊和低電磁輻射的設計上,就能將最後階段的重新設計成本和產品出貨日期的延誤減到最小。

開發人員在開始設計時應該做到幾件事:首先就是強大可靠的電源,讓就算負載動態改變也能將開關雜訊減到很小。還有,將高速訊號線之間的串訊(Crosstalk)減少、提供高頻和低頻解耦合、確保傳輸線效應最小,就能提供良好的訊號完整性。一般來說,開發人員只要達到上述目標,就能避免雜訊和電磁干擾的影響。

雜訊影響品質甚鉅

將雜訊降到最低是高速DSP系統設計最重要的要件之一。任何過大的雜訊源都會造成隨機邏輯和鎖相迴路(PLL)失效,使系統可靠性下降,甚至可能產生電磁輻射,影響產品通過FCC相容性測試。另外,雜訊過大的系統也很難進行除錯,即便雜訊有辦法消除,整個過程也可能要多次重新設計電路板。

在影音系統裡,即使很小的干擾都會對終端產品效能造成明顯衝擊。舉例來說,許多因素,如音訊編/解碼器的品質、電源供應雜訊、電路板布局和相鄰電路間的串訊強度,都有可能影響音訊錄製和播放效能。除此之外,取樣時脈的穩定度也必須很高,才能避免播放和錄製時出現不必要的爆裂音和喀嚓聲。

視訊系統的主要挑戰則是消除色彩失真、60Hz嗡聲和音訊拍差(Beat)等瑕疵,這些瑕疵會對監控應用等要求最高畫質的系統造成不利影響。這些問題通常與視訊電路板設計不良有關,例如電源供應雜訊進入視訊數位類比轉換器(DAC)的輸出、音訊播放造成電源供應出現暫態(Transient)或是音訊電路與視訊電路的高阻抗線路產生訊號耦合。

某些典型的視訊問題來源包括同步與畫素時脈過衝(Overshoot)和下衝(Undershoot)、編碼解碼器與畫素時脈抖動,使色彩訊號受到影響、未接終端電阻所造成的影像失真以及音訊和視訊隔離不佳而造成的畫面閃動。

雜訊問題對許多需要低位元錯誤率的通訊系統,如影音應用都會造成影響。這類通訊系統的電磁輻射不僅會產生電磁干擾,還會影響其他的通訊通道,進而造成通道偵測錯誤。這些問題可藉由適當技術加以解決,包括採用適當電路板設計、電磁屏蔽、以及將射頻訊號與類比/數位混合訊號隔離。

控制雜訊勢在必行

高速DSP系統有許多潛在的開關雜訊來源,包括訊號線路間的串訊、傳輸線效應造成的訊號反射、解耦合電容不適當而造成電壓下降、高電感性的電源供應線路、振盪器和PLL電路、交換式電源供應、線性穩壓器不穩定所造成的大電容性負載與磁碟驅動電路等。

這些問題來自於電路耦合和電磁耦合。電路耦合是因為相鄰訊號和電路之間存在著寄生電容和互感,電磁耦合則是由於訊號線路實際上已變成天線所造成。如果電磁輻射很強,它還可能造成電磁干擾而影響其他系統。

高速DSP系統的雜訊雖無法完全消除,卻能減到最小。電子零件的內部都有雜訊源,故須仔細考慮元件特性和選擇正確的元件。除了選擇元件外,電路板布局和迴路解耦合等兩種常用技術也能控制系統雜訊。良好的電路板布局不僅降低雜訊路徑出現的機率,還會將進入訊號線和電流迴路區的電磁輻射降到最低。解耦合能防止雜訊影響相鄰的電路--雖然設計人員能讓相鄰電路不受雜訊影響或消除雜訊耦合管道,但最好的做法還是從源頭消除雜訊。

以下將介紹幾種常用來解決系統雜訊和電磁干擾問題的技術。

|

|

| |

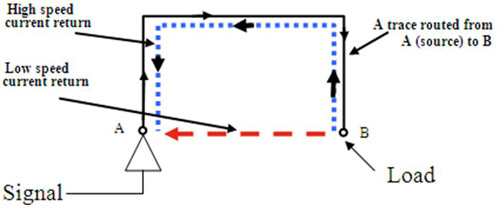

如圖1所示,低速訊號電流會通過阻抗最小的路徑,也就是最短的路徑回到源頭。而高速訊號電流則會通過電感最小的路徑,也就是迴路面積最小的路徑。

|

| 圖1 高速與低速電流迴路比較 |

因此,高速設計的目標之一,是為訊號電流安排電感最小的路徑,這可藉由電路板的電源面和接地面來實現。電源面對高頻訊號就像解耦合電容,可將寄生電感降到最低。接地面則會產成俗稱鏡像面(Image Plane)的屏蔽效應,可提供最短的電流迴路。

好的電路板布局應讓接地面靠近電源面,以產生更大的接地面電容和更小的電感,協助降低雜訊和電磁輻射。為了屏蔽電磁干擾,重要訊號路徑最好在接地面的旁邊,其次是在電源面的旁邊。

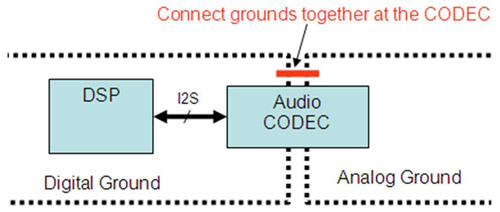

高速視訊系統則不應將視訊訊號的地線隔離,這樣才能縮短迴路的長度。類比音訊訊號的地線雖須隔離,卻應如圖2所示,在資料輸入點將類比訊號的地線短路到數位訊號的地線。

|

| 圖2 音訊接地隔離 |

|

|

|

| |

訊號之間的相互干擾又稱為串訊,可能來自訊號線間的電磁輻射,或由電源面及接地面上傳播的不必要訊號所產生。串訊與訊號線間距的平方成反比,因此,單端訊號間的距離最少應為訊號線寬度的兩倍,以便將干擾降到最低。乙太網路和USB等差動訊號的距離則須與訊號線的寬度相同,確保差動阻抗能相互配合。重要訊號則可透過接地面和電源面屏蔽,或是額外增加一條平行的地線。

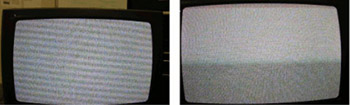

訊號產生的高頻諧波也會造成串訊。由於輻射能量與訊號的上升及下降時間成正比,上升或下降時間越慢,產生的干擾就越低。圖6為內部時脈訊號的電磁輻射所造成視訊干擾的例子。在北美地區,18.432MHz音訊時脈的第三諧波會落在頻道2的頻譜,造成圖6左方的干擾。但若能在音訊時脈訊號線路上增加一個串聯電阻,就能減緩上升和下降時間,進而如圖6右方將干擾消除。設計人員必須了解時脈訊號的邊限,確保其上升和下降邊緣在系統限制範圍內。

|

| 圖6 解決影音串訊的問題 |

|

|

|

| |

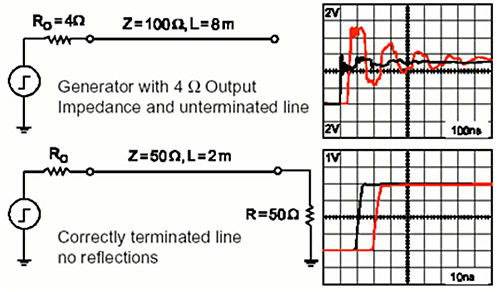

當高速訊號線變成發射機並產生電磁輻射時,傳輸線效應同樣會造成串訊問題。一般而言,當訊號的上升時間小於傳播延遲時間的兩倍時,訊號線就會產生電磁輻射。這個規則表示訊號線應越短越好,才能將傳播延遲時間降到最低。另一個規則是要為訊號線路提供終端匹配,以便減少上升時間,使訊號反射造成的過衝和下衝降到最低。圖7顯示並聯終端阻抗如何修正電壓位準,讓傳輸線效應降到最低。

|

| 圖7 終端阻抗將傳輸線效應降到最低 |

設計人員或許會不確定是否要在元件的內部已提供終端阻抗時在外接終端電阻。其實外接終端電阻除了能控制傳輸線效應外,還能對訊號完整性進行微調,這是一項很有用的功能,因為DSP不能與電路板阻抗完全相容;此外,終端電阻還能降低供應電流以及上升和下降時間。

外接提升和下拉電阻的重要性不下於外接終端電阻。雖然內部提升和下拉電阻就足以應付空接的接腳,高速開關雜訊仍可能進入並連接至外部電路的接腳,並誤觸這些接腳的邏輯電路。為了避免這個問題,重要訊號接腳都應該外接提升和下拉電阻。 |

|

|

| |

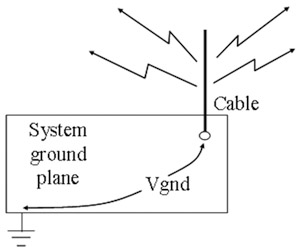

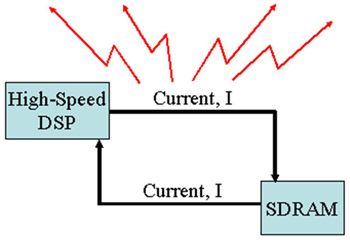

電磁輻射離開系統機殼後便成為電磁干擾,並可能導致設計無法通過主管單位的認證。電磁輻射可分為兩大類,一種是共模輻射(Common Mode),此時發射機為一條筆直的訊號線或纜線;另一種為差動模式輻射,此時訊號及其迴路形成一個很大的電流迴路。共模輻射強度會隨著頻率升高而降低,差動模式輻射則會隨著頻率而增加,直到達飽和點為止。這兩種模式如圖8和圖9。

|

| 圖8 共模輻射 |

|

| 圖9 差動模式輻射 |

電磁干擾的處理方式須視其來源而定。以共模輻射為例,若電磁干擾來自外接的纜線(圖8),通常會在纜線上增加一個線圈。而電磁干擾若是由系統內部的傳輸線效應造成,則通常會在線路上增加終端阻抗,但有時在訊號線之間增加接地線也能降低電磁輻射。另一種解決方法是將訊號線長度縮短至訊號波長的二十分之一以下。舉例而言,若訊號線上正傳輸500MHz的訊號,則其長度就不應超過1.18英吋,才能避免傳輸線效應。

在差動模式發射機中,輻射能量為電流、迴路面積及頻率的函數。此時,要將電磁輻射降到最低的方法包括連接終端阻抗以降低電流、提供適當的訊號電流迴路來減少迴路面積、或是降低電路的操作頻率。 |

|

|

| |

計算解耦合電晶體時,也須將動態電流列入考慮。高速電流會不斷變化,其中許多暫態變動都可能造成電磁輻射。此外,設計人員也可改變電容值,防止電容自諧振而對頻率範圍造成限制。採用多層電路板是很好的解決方案,因為電源面對高頻訊號有解耦合的效果,接地面則提供最短的迴路。高速訊號必須加以隔離,繞線時也要遠離其他訊號,最好不要將接地面隔離。雖然複雜且具不必要特性的系統設計會導致雜訊與電磁輻射,類似前述的技術仍能有效將其控制。

高速DSP視訊系統有許多潛在的雜訊和電磁干擾源,可能影響系統操作或導致設計無法通過主管機關認證。幸而設計人員只要規畫和深入瞭解雜訊及電磁輻射的來源,就能將這些問題降到最低。設計人員只要在設計初期時多費一些工夫,就可避免事後花費大量時間進行除錯及解決問題。電路板布局和迴路解耦合是常用來限制系統雜訊和電磁干擾的兩種技術,可協助DSP視訊設計人員有效解決系統雜訊和電磁輻射的問題。 |

(本文作者任職於德州儀器)