繼行動裝置之後,物聯網應用已躍居晶圓廠新的技術布局焦點,包括台積電、聯電和三星皆相繼揭櫫16/14奈米FinFET製程進展,並加速朝10奈米以下先進製程邁進,以實現更高整合度、更低功耗和占位空間的次世代晶片,搶占物聯網產品設計商機。

1x奈米製程戰火一觸即發。穿戴式電子、物聯網裝置設計熱潮興起,已驅動先進製程導入需求,因而刺激台積電、聯電和三星(Samsung)等晶圓代工業者加足馬力發展16/14奈米鰭式電晶體(FinFET),並於近期頻頻發動攻勢。

其中,台積電一馬當先發布超低耗電(ULP)技術平台,提供從0.18微米到16奈米鰭式電晶體(FinFET)等一系列超低耗電製程,協助客戶打造更低功耗且整合度更高的系統元件。至於聯電和三星也不落人後,前者透過與半導體設備商合作,展開14奈米製程產線先期部署,後者亦積極展現14奈米FinFET製程設計實力,讓市場頓時硝煙瀰漫。

台積電董事長張忠謀曾表示,物聯網將是電子產業下一個大事(Next Big Thing),並點名低功耗、系統級封裝(SiP)及感測技術將是支撐物聯網發展的三大支柱。其中,低功耗設計更已成為半導體供應鏈業者一致追求的目標,將牽動一連串製程、IC設計技術轉變。

發動物聯網首波攻勢 台積電祭出超低耗電製程

物聯網和穿戴式電子裝置對晶片耗電量的規格要求遠勝於行動裝置,因此,台積電日前已將適用於行動元件製造的低耗電製程,進一步升級為可滿足下世代物聯網和穿戴電子晶片設計的超低耗電製程,並組成覆蓋多元節點和應用的技術平台,以因應各類型元件研發需求。

台積電已預計在2014年底前與客戶達成數項設計合作案,包括55奈米、40奈米及28奈米超低耗電製程,並將於2015年展開試產。

據悉,超低耗電技術平台涵蓋0.18微米極低漏電製程(0.18eLL)、90奈米超低漏電製程(90uLL)及16奈米FinFET製程,且能支援高達1.2GHz運算速度;針對特殊製程應用,台積電更在該平台納入嵌入式記憶體專用的55奈米超低耗電製程(55ULP)、專攻射頻元件的40奈米超低耗電製程(40ULP),以及鎖定SoC設計的28奈米超低耗電製程(28ULP)。

相較前一代製程方案,超低耗電技術平台將可實現更高層級的晶片系統整合,並降低晶片操作電壓達20~30%,大幅減少動態與靜態功耗,以延長系統電池使用時間達二至十倍。台積電總經理暨共同執行長劉德音強調,低功耗及無所不在的連結功能已是物聯網成功的關鍵,而台積電搶先業界推出完備的超低耗電技術平台,將有助催化物聯網技術發展與創新。

此外,晶片商亦可充分利用台積電開放創新平台(OIP)所提供的矽智財(IP)設計生態環境,為使用超低耗電技術平台的產品增添許多功能應用價值。

益華電腦(Cadence)資深副總裁暨策略長徐季平指出,看好台積電超低耗電技術平台在物聯網晶片市場的發展潛力,益華也積極爭取合作機會,並已成功將旗下記憶體、類比、介面、基頻、影音處理和臉部辨識等IP及相應開發工具,置入超低耗電技術平台,可望協助晶片商提升產品功能和上市速度,迎合物聯網和穿戴電子快速改朝換代的生命週期。

舉例來說,當晶片開發人員欲進行全新的超低耗電製程設計時,可重覆利用製程矽智財與元件資料庫,以提高首次設計即生產成功的機率,達到產品迅速上市的目標。

在台積電登高一呼下,全新的物聯網製程技術大聯盟正逐漸成形。不過,因應物聯網裝置對效能、功耗和尺寸要求日趨嚴格的局面,晶圓代工業者亦須加緊展開下一步技術布局,遂紛紛將目光聚焦於16/14奈米FinFET方案。

卡位1x奈米黃金世代 晶圓廠投資火力全開

台灣晶圓雙雄近期分別攜手矽智財(IP)商和半導體設備廠,衝刺16/14奈米FinFET製程。其中,台積電已正式試產16奈米晶片,而聯電則引進新的電腦整合製程(CIM)軟體以加快建置14奈米產線。

台積電表示,該公司與安謀國際(ARM)的技術合作,已推進至16奈米FinFET製程,近期雙方亦共同在2014年台積電OIP生態系統論壇,以及ARM TechCon大會中,展出新一代64位元Cortex-A57與Cortex-A53晶片驗證成果,並設定於明年上半年投產的目標。

台積電研究發展副總經理侯永清指出,台積電係首家在FinFET製程上完成ARM big.LITTLE架構實作驗證的晶圓廠,雙方的合作亦將延續至下一代製程,以持續滿足業界對行動運算、伺服器效能及功耗表現的要求。

據悉,台積電正緊鑼密鼓布局更先進的16奈米FinFET+製程,預計在2014年第四季推出,相較於前一代方案,新製程可在相同功耗下,提升11%的Cortex-A57處理器效能,而運用到Cortex-A53處理器,則可在支援低運算密度應用時再降低35%功耗,可望發揮極致的晶片動態效能與節能優勢,迎合物聯網的發展。

值得注意的是,台積電為鞏固晶圓代工一哥的地位,已搶先與ARM合作規畫10奈米FinFET製程發展藍圖(表1),並開始投入先期研究工作,一舉拉高技術競賽層次。據悉,雙方自現在開始,累積約1年以10奈米製程生產64位元實體IP與設計法則的經驗後,最快在2015年第四季即能協助客戶完成10奈米處理器設計定案(Tape-out)。

與此同時,聯電也加碼投資14奈米FinFET製程,並在旗下12吋廠導入應用材料(Applied Materials)的工廠自動化軟體,提高晶圓生產力及良率,宣示其14奈米量產腳步將至。

事實上,晶圓廠面對日益複雜的電晶體架構和晶片電路設計,須仰賴精密材料工程設計、製程及多項互動變數控制技術,因此聯電遂引進應用材料專為整廠設計的電腦整合製程平台,包括FactoryWorks製造執行系統(MES)、設備工程系統(EES)、產能即時分配/管理,以及用於生產規畫和模擬的自動化軟體工具,用於檢視整廠製造流程,並透過主動決策減少製程變異,以同步提升工廠自動化細膩程度、生產效率和良率。

至於三星(Samsung)也窮追不捨,同樣藉由2014年ARM TechCon的舞台,展示其14奈米產品火力,並已與ARM攜手完成測試晶片,與台積電較勁的意味濃厚。

儘管近期三家晶圓代工廠接連釋出1x奈米先進製程研發成果,然而要邁入量產,還須克服生產良率、速度和成本等諸多挑戰。尤其在製程節點大幅微縮、電路線距更加緊密的情況下,晶圓製造關鍵的微影技術更是首當其衝,正面臨設備和技術革新聲浪。

浸潤式/EUV微影雙管齊下1x奈米演進一路暢通

|

| 圖1 ASML亞太區技術行銷協理鄭國偉認為,混合式微影製程將是延續摩爾定律發展的關鍵技術。 |

為順利推動16/14奈米FinFET,以及未來的10/7奈米先進製程,晶圓廠正加緊研發極紫外光(EUV)微影技術,並計畫以浸潤式(Immersion)微影搭配EUV的混搭方式,達到兼顧高解析度曝光和高速/低成本生產效益的目標。

艾司摩爾(ASML)亞太區技術行銷協理鄭國偉(圖1)表示,由於浸潤式微影技術的解析度無法滿足1x奈米製程需求,因此業界正不斷加碼投資新一代EUV微影方案,以達成十倍以上解析度,持續延伸摩爾定律(Moore's Law)的發展。不過,EUV機台相對昂貴,晶圓廠基於成本考量,僅將在晶圓關鍵層(Critical Layer)導入EUV技術,並於非關鍵層沿用浸潤式微影,因而揭開全新的混合式微影製程模式。

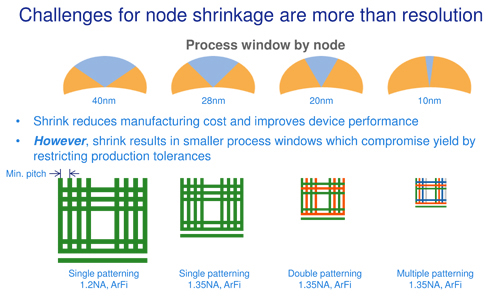

事實上,在跨入1x奈米前,半導體產業在20奈米世代就先掀起一波微影技術革新潮。鄭國偉指出,20奈米晶圓單位面積內的電晶體數量激增,且電路線距更緊密(圖2),已導致原先單次曝光的浸潤式微影製程不敷使用需求,遂使業界全面轉向雙重曝光(Double-Patterning)形式,以確保益趨複雜的電路能完整顯影在晶圓上。接續20奈米腳步,16/14奈米FinFET挑戰將更為艱鉅,業者除須發展三重曝光外,還須強化影像疊對控制(Overlay Control)、量測及校正能力,方能順利投產。

|

| 圖2 半導體製程演進首要面對的挑戰為Process Window大幅縮小,晶圓廠須引進更高解析度的微影設備才能解決。 |

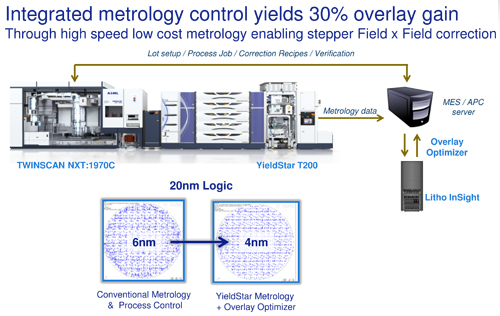

鄭國偉指出,雙重/三重曝光意味著要進行多次光罩製程,相較於傳統單次曝光,其產生對位誤差而影響晶圓良率的風險將大幅攀升,且多道製作程序亦將加重生產速度和成本壓力,因此對晶圓廠和微影設備開發商而言,如何提升雙重/三重曝光微影設備的製程適用範圍控制(Process Window Control)精準度,並能即時偵測出影像對位誤差或參數漂移情形進行校正,已是當務之急。

|

| 圖3 微影設備整合量測系統將能即時校正,提升製程控制精確度。 |

也因此,ASML在傾力開發EUV技術的同時,也不斷針對浸潤式微影應用精益求精,並已於近期推出一套整合曝光機(Scanner)、量測系統和電腦輔助設計軟體的全方位微影解決方案(Holistic Lithography),協助晶圓廠提升製程控制能力,並透過縝密且自動化的量測和校正,確保多次微影製程的影像疊對精確度,以優化生產良率及成本。

鄭國偉強調,新型浸潤式、EUV微影設備,以及未來的混合式微影技術,皆將成為半導體製造業從20奈米邁向16/14奈米FinFET和10奈米以下先進製程的關鍵利器,重要性將不容忽視。

顯而易見,半導體製造業已鎖定物聯網的發展,亦步亦趨布局新技術,不僅加速驅動製程翻新,也將為業界創造更多設計商機。