當載體和電纜供應商開始向客戶推出語音、數據、視訊和隨選視訊(Video on Demand, VoD)服務時,原始設備製造商正全力開發基於網際網路通訊協定(IP)的系統,包括被動式光纖網路(PON)、CMTS(Cable Modem Termination System)、IP、數位用戶線路多工接取器(DSLAM)以及其他的接入和最後一哩設備。

目前普通的基礎物理層對IP系統使用普及的乙太網路技術與高級服務品質(Quality of Service, QoS)覆蓋結合,工程師正投入更多努力將交換乙太網路背板連接到系統線卡,特別是網路處理器。系統設計師常選擇乙太網路交換機和具有獨立性的網路處理器,而鮮少考慮兩者互聯帶來的挑戰,工程師僅須解決開發橋接器、整合解決方案和節約成本實現設計的難題,而由於介面以極高速率運行,所以必須關注功耗的發展。

完整XAUI埠具低功耗

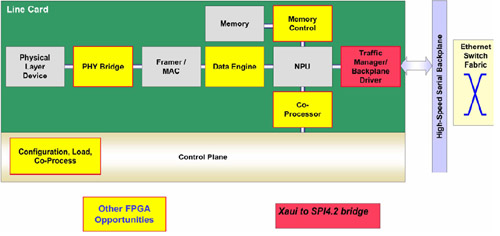

基於典型的乙太網路的系統結構由乙太網路交換機所組成,依次由幾個連接到一連串的基於網路處理器的線卡的10Gbit/s鏈路組成(圖1)。在10Gbit/s交換系統,乙太網路交換機結構提供一系列XAUI(Ten Attachment Unit Interface)埠。每個XAUI埠有四個3.125Gbit/s串列/解串器(SerDes)。這些序列埠通過背板或者中間結構完美地連接到線卡。

|

| 圖1 乙太網路系統結構 |

有些乙太網路交換機包括埠交換、流量控制或者用於服務品質要求的位址資訊,在原來的乙太網路標準中沒有服務品質要求的內容。

為了保持10G線速,這些XAUI埠的運行速率得高於指定的每個通道3.125Gbit/s的速率。運行在3.75Gbit/s的博通(Broadcom)HiGig+協議就是一個例子。運行這些所有權協定時,額外的開銷允許客戶開發自行定義的應用交換,通過網路智慧地傳遞通訊量。此外,針對基於IP的應用,這些交換堆疊協定具有無約束的可量測性。

SPI4.2介面運行速度高

擁有網路處理器的線卡常用SPI4.2介面,SPI4.2運行速率可超過10Gbit/s的高速平行介面,用於網路處理器、通訊量管理器、媒體接入控制(MAC)等。SPI4.2使用並行的十六位元寬的低電壓差動訊號傳輸(LVDS)發送和接收源同步介面,為了處理流量控制,在狀態通道有額外的構造。在SPI4.2鏈路上發送的資料作為一個封包,或者突波的多個封包,並擁有控制頭描述每個突波。

每個封包控制頭還有識別與突波資料相關的SPI4.2通道,這些位元可用來將整個鏈路分割成各種通道,SPI4.2規範支援每個鏈路多達兩百五十六個通道,很明顯地在SPI4.2和XAUI間存在著很大的物理和協定差異,因此SPI4.2介面必須橋接至XAUI鏈路。

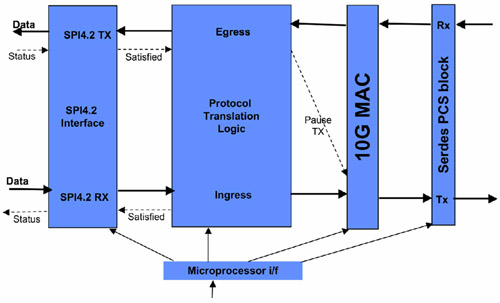

為了將XAUI(或者更快時鐘的XUAI)鏈路連接到SPI4.2介面,須構建一個能夠引導資料通過四個主要單元的橋接器。針對XAUI至SPI4.2橋接器,主要單元為XAUI、10G MAC、協定轉換邏輯與SPI4.2介面。此外,還要有微處理器介面,用來配置每個橋接器的單元(圖2)。

|

| 圖2 連接到SPI4.2介面的XAUI(或更快時鐘的XUAI)鏈路 |

XAUI SerDes區塊必須連接到四個3.125Gbit/s資料通道。這個邏輯只需要四個接收和四個發送訊號,運行速度非常快,但消耗相當大功率,所以必須謹慎選擇每個通道消耗大約一百毫瓦功率的SerDes。在四個SerDes通道,每一個通道都要對齊,以保證跨越所有通道的資料同步可獲得聚集為10Gbit/s的串列傳輸速率,這動作由XAUI狀態機負責處理。

在與SerDes混合的許多元件的物理編碼子層(PCS)中,這個邏輯是很普通的。從四個通道中提取10Gbit/s的資料後,須以XGMII介面格式化。這是針對10Gbit/s以156MHz運行的六十四位元匯流排,或者針對12Gbit/s以187MHz運行。 XGMII是802.3ae標準,用於格式化源於物理層到10G MAC的10Gbit/s資料。利用含有SerDes後緊跟PCS區塊的現場可編程閘陣列(FPGA)是理想的選擇,採用這種結構可直接格式化XAUI資料至XGMII,能節省邏輯與功耗。

10GbE MAC處理大至小封包

10G MAC邏輯接收XGMII資料並提取乙太網路的封包框。首先由10G MAC識別Packet SOP的起始和Packet EOP頭的結束。由於乙太網路的資料以可變大小的封包發送,MAC須能夠處理各種大小的封包,包括8K長度的巨型封包。一旦恢復了資料,進行循環多餘碼檢查(CRC)校驗保證資料的完整性。資料進入MAC時,在接收端做這項工作。

若CRC校驗失敗,丟棄壞的封包框並建立錯誤標誌。在發送端MAC須產生CRC碼,MAC還須保持對資料的統計,支援管理資訊資料庫。

此外,10G MAC還有對接收到的封包進行位址過濾的功能,可以有幾個過濾選擇取決於終端用戶的應用。而從MAC流出被允許通過橋接器,但未經過濾的封包會寫入六十四位元寬的先進先出(FIFO),再送至協定轉化邏輯。

儘管在FPGA中可實現10G MAC,但須用到四千多個查表(LUT),因此會消耗許多功率。作為選擇的方法,相對基於FPGA的實現,選用特定應用積體電路(ASIC)製程嵌入式10G MAC的功率可減少50%,如此就有充裕的FPGA來實現用戶邏輯。

FPGA提高流量控制彈性

乙太網路封包通過10G MAC的位址過濾標準,進入六十四位元FIFO之後,協定邏輯轉換六十四位元的FIFO邏輯,並在通過其到達SPI4.2介面前,將它轉換為一百二十八位元。在協定邏輯中,這些FIFO用來控制接收和發送方向的資料流程。

如果通訊發生擁塞,10G MAC與協定邏輯一起保證資料封包框停止。還有一個微處理器介面可通過各種控制寄存器調整流量控制。經過標準的Ethernet X_ON,X_OFF流控制命令,協定邏輯控制至10G MAC的流量,於是協定邏輯間接地轉換流量控制到基於SPI4.2的狀態命令。

SPI4.2狀態模式受青睞

SPI4.2有兩個方案在一個鏈路裏實現流量控制。一個是基於Credit的流程,即對每個通道,Credit在鏈路的每一方進行交換,如果接收方通道很擁塞的話,將不再給予發送方Credit,直到擁塞被清除。第二個流量控制方案是基於狀態,在此模式下報告排隊的狀態,如Starved或Satisfied,佇列中充滿資料時停止傳送。基於狀態模式的流量控制用得較多,也較易被實現,如萊迪思(Lattice)SPI4.2至XAUI橋接器的IP使用基於狀態的流量控制。

舉例來說,橋接器進入方向是從網路處理器到乙太網交換機。網路處理器完成其封包時,會詢問其狀態通道的狀態。可能的狀態是Starved/Hungry或Satisfied,這是由橋接器內的入口FIFO的集合電路板上微處理器介面的流量控制寄存器來決定。

若不要求流量控制,網路處理器會初始化傳輸,並傳送封包到橋接器的SPI4.2接收介面,封包進入橋接器時,進行一百二十八到六十四位元資料寬度轉換,資料寫入入口FIFO,具有用戶可編程臨界值支援存儲、發送和切入操作,一旦超過用戶可編程傳送臨界值,橋接器將會告知10G MAC一個封包有效。

若10G MAC校驗XAUI介面流量控制的狀態是無效的話,橋接器將傳送這個封包,在出口方向的流量控制有相似的資料流程,但須將出口FIFO臨界值設置到較高,以便提供SPI4.2通過XAUI的較高頻寬,例如運行HiGig+產生12Gbit/s的頻寬。然而SPI4.2介面經常運行400M~500MHz DDR,提供12.8G~16Gbit/s,因為流量控制邏輯是用FPGA與內置記憶體區塊來實現的,因此可以提供更複雜的方案。

聚集多個乙太網路通道

涉及協定轉換邏輯的前述討論假設10Gbit/s源於單個10G管道,對於許多網路處理器到乙太網交換機來說是足夠的。然而某些設計中,10Gbit/s或12Gbit/s管道須要分成多個通道。例如一個乙太網路交換聚合十二個1Gbit/s乙太網線,也許要求協定轉換邏輯將12Gbit/s管道分割成十二個通道。另外一例是線速率超負荷,若二十四個鏈路的總頻寬小於12Gbit/s聚合頻寬,那麼或許要分割二十四個通道,這些額外的通道需要更多的FIFO和邏輯來管理。橋接器的設計須要考慮配置的類型,無論用一個或者多個通道,資料必須通過協定邏輯到SPI4.2介面,再到網路處理器。

SPI4.2功耗與動態對齊

SPI4.2從FIFO讀數據或者寫資料至FIFO,於是經十六位元同步SPI4.2線突波資料。為了達到很高且可靠的SPI4.2速度,大多數高性能網路處理器將進行動態對齊。

動態對齊介面即是資料位元可依據時鐘進行移入。使用動態對齊時,十六個LVDS I/O中,每一個皆可運行達1Gbit/s,總計最大吞吐量為16Gbit/s(16×1Gbit/s)。因為這個介面以極高速度運行,通常要消耗數瓦,更不用提FPGA中的上千個LUT所費功耗。由於有了10GbE MAC,將FPGA與ASIC的SPI4.2邏輯互相混合為最佳選擇。嵌入式SPI4.2核心節省數千個LUT,並將功耗減低至約一瓦。

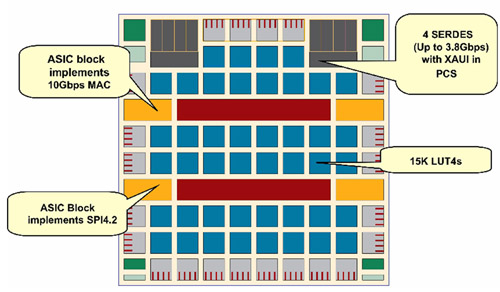

對於許多基於乙太網路交換機的系統,XAUI至SPI4.2橋接器是必要的。FPGA的價值是提供靈活選擇任何數量的網路處理器和乙太網交換元件,提供用戶化的橋接方案,完成聚合多個乙太網路流量,以及在同一元件上實現多個橋接器。然而設計總要考慮成本,橋接器解決方案的低成本、低功耗、消耗較少資源的特點將為關鍵,如萊迪思SCM FPGA系列混合實現10G MAC和SPI4.2介面的硬體ASIC塊,其餘的FPGA邏輯和記憶體有足夠的資源來實現橋接功能,要求單個通道SPI4.2至XAUI(或者相關的基於乙太網路協定)橋接器時,緊密的17毫米×17毫米、兩百五十六個球型微間距BGA封裝的SCM15 FPGA(圖3)可實現完整的低功耗、低成本且小型化設計。

|

| 圖3 SCM15 FPGA結構 |

(本文作者任職於萊迪思)